# Analysis and Design of Sequential Digital Systems

# **Analysis and Design** of Sequential Digital Systems

- Other titles in Electrical and Electronic Engineering

- G. B. Clayton: EXPERIMENTS WITH OPERATIONAL AMPLIFIERS

- G. B. Clayton: LINEAR INTEGRATED CIRCUIT APPLICATIONS

- J. C. Cluley: ELECTRONIC EQUIPMENT RELIABILITY

- R. F. W. Coates: MODERN COMMUNICATION SYSTEMS

- A. R. Daniels: INTRODUCTION TO ELECTRICAL MACHINES

- C. W. Davidson: TRANSMISSION LINES FOR COMMUNICATIONS

- W. Gosling: A FIRST COURSE IN APPLIED ELECTRONICS

- B. A. Gregory: AN INTRODUCTION TO ELECTRICAL INSTRUMENTATION

- Paul A. Lynn: AN INTRODUCTION TO THE ANALYSIS AND PROCESSING OF SIGNALS

- A. G. Martin and F. W. Stephenson: LINEAR MICROELECTRONIC SYSTEMS

- R. G. Meadows: ELECTRICAL COMMUNICATIONS THEORY, WORKED EXAMPLES AND PROBLEMS

- J. E. Parton and S. J. T. Owen: APPLIED ELECTROMAGNETICS

- A. Potton: AN INTRODUCTION TO DIGITAL LOGIC

- J. T. Wallmark and L. G. Carlstedt: FIELD-EFFECT TRANSISTORS IN INTEGRATED CIRCUITS

- G. Williams: AN INTRODUCTION TO ELECTRICAL CIRCUIT THEORY

# Analysis and Design of Sequential Digital Systems

## L. F. Lind

Department of Electrical Engineering Science, University of Essex

### J. C. C. Nelson

Department of Electrical and Electronic Engineering, University of Leeds

© L. F. Lind and J. C. C. Nelson 1977

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission

First edition 1977 Reprinted 1979

Published by

THE MACMILLAN PRESS LTD

London and Basingstoke

Associated companies in Delhi Dubin

Hong Kong Johannesburg Lagos Melbourne

New York Singapore and Tokyo

ISBN 0 333 19266 4 (hard cover) 0 333 19267 2 (paper cover)

Set in Monophoto Times by Doyle Photosetting Ltd, Tullamore, Ireland Printed by Unwin Brothers Limited, The Gresham Press, Old Woking, Surrey.

This book is sold subject to the standard conditions of the Net Book Agreement.

The paperback edition of this book is sold subject to the condition that it shall not, by way of trade or otherwise, be lent, re-sold, hired out, or otherwise circulated without the publisher's prior consent in any form of binding or cover other than that in which it is published and without a similar condition including this condition being imposed on the subsequent purchaser.

# Contents

| Pr | eface |                                            | vii |

|----|-------|--------------------------------------------|-----|

| 1. | Intr  | roduction                                  | 1   |

|    | 1.1   | What are Digital Systems                   | 1   |

|    | 1.2   | <u> </u>                                   |     |

|    | 1.3   |                                            | 2 3 |

|    | 1.4   | · -                                        | 4   |

|    | 1.5   | Comparison of Analogue and Digital Systems | 4   |

| 2. | Rev   | iew of Combinational-logic Techniques      | 5   |

|    | 2.1   | Logic Levels                               | 5   |

|    | 2.2   | Gates                                      | 6   |

|    | 2.3   | The Karnaugh Map                           | 12  |

|    | 2.4   | Partitioning                               | 20  |

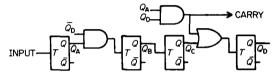

|    | 2.5   | Iterative Circuits                         | 22  |

|    | 2.6   | Multiple Outputs                           | 23  |

|    | 2.7   | Concluding Remarks                         | 24  |

|    | 2.8   | Examples                                   | 24  |

|    | Ref   | erences                                    | 28  |

| 3. | Intr  | roduction to Sequential Systems            | 29  |

|    | 3.1   | Fundamental Concepts                       | 29  |

|    | 3.2   | Storage Devices                            | 32  |

|    | 3.3   | Sequential Sub-systems                     | 38  |

|    | 3.4   | Intuitive Design of Sequential Systems     | 47  |

|    | 3.5   | Examples                                   | 49  |

|    | Ref   | erences                                    | 53  |

| 4. | Asy   | nchronous Sequential Systems               | 54  |

|    | 4.1   | Basic Concepts                             | 54  |

|    |       | Analysis Techniques                        | 57  |

|    | 4.3   | Races and Hazards                          | 63  |

|    | 4.4   |                                            | 68  |

|    | 4.5   | Examples                                   | 87  |

|    | Ref   | erences                                    | 102 |

| <b>T</b> 7 | 1 |

|------------|---|

| v          |   |

#### CONTENTS

| 5.  | Syn   | chronous Sequential Systems                         | 104   |

|-----|-------|-----------------------------------------------------|-------|

|     | 5.1   | Advantages and Disadvantages of Synchronous Systems | 104   |

|     | 5.2   | Preliminary Design                                  | 106   |

|     | 5.3   | Flow-chart Method of Design                         | 109   |

|     | 5.4   | Pictorial Aids                                      | 119   |

|     | 5.5   | State Assignment                                    | 124   |

|     | 5.6   | Examples                                            | 126   |

|     | Refe  | erences                                             | 131   |

| 6.  | Prac  | ctical Design Considerations                        | 132   |

|     | 6.1   | Initial Specification                               | 132   |

|     | 6.2   | Detailed Design                                     | 132   |

|     | 6.3   | Prototype Development                               | 134   |

|     | 6.4   | Printed-circuit Boards                              | 134   |

|     | 6.5   | Testing and Documentation                           | 136   |

|     | 6.6   | Conclusion                                          | , 136 |

|     | Ref   | erences                                             | 137   |

| Ap  | pendi | x                                                   | 139   |

| Inc | lex   |                                                     | 141   |

## **Preface**

This text presents the basic information required for successful design of modern logic systems. The information is presented in a form that should be immediately applicable by practising engineers but that also forms the basis of a comprehensive final-year university or polytechnic course. It will also prove useful to postgraduates in disciplines relying on the application of digital methods, for example, computer science, control engineering and instrumentation.

Certain mathematical theorems relating to Boolean variables are excluded for over-all clarity. The use of these theorems to simplify Boolean expressions has, in large part, been superseded by mapping and tabular techniques. Excessive treatment of the mathematical basis of some of the procedures would tend to obscure the engineering concepts involved.

The theoretical material is illustrated with practical examples wherever possible. The examples can be used for extending the reader's knowledge from the particular to the general, which, in many cases, appears to be a more natural approach than the reverse. Wide use of references is made where this is felt desirable, to free the text from detail not immediately relevant and to provide a basis for further reading.

An important feature of the book is the consideration of logic design from a human point of view. An attempt is made to relate the more formal design techniques to the widely used intuitive or 'cut-and-try' approach. For example, the problem of state assignment is simplified by considering only those possibilities that fit in with a natural (or human) approach to the problem. This consideration has repercussions in all phases of the design procedure. One of the most important results lies in the increased understanding of the operations of the circuit by service personnel. Also, by requiring the solution to look 'natural', the number of possibilities is greatly reduced (sometimes to one), thereby reducing the amount of design time required.

The partitioning of one complex circuit into a number of smaller circuits is also carefully considered. To date there is no automatic procedure for doing this; instead, ad hoc solutions are generally used. Guidelines are laid down for accomplishing this partitioning in this book. Again, 'naturalness' is the keynote of the partitioning procedure. A well-partitioned circuit should be relatively simple to test and troubleshoot, which leads to enormous practical advantages in the post-design career of the circuit.

viii PREFACE

Particular attention is devoted to hazards, races and other phenomena that, although not apparent from a superficial appraisal of a proposed design, can lead to mal-operation. Careful attention to these points, together with the information provided in the final chapter on practical implementation, should lead to the production of reliable designs every time.

The authors would like to thank R. Coleman, Technical Director of Trend Communications Ltd, for his assistance with chapter 6. They would also like to thank Mrs S. Nelson for her accuracy and patience in typing the manuscript.

# Introduction

Digital systems are not new. The simple 'on-off' signalling techniques used by nineteenth-century telegraphers are one example of an early application of digital techniques. However, for many years development of the various applications of digital principles continued virtually independently; construction of electromechanical telephone exchanges, for example, progressed quite independently of the development of digital computing systems.

Two factors have influenced the present importance of digital-system design as a discipline in its own right. One is the development of design procedures—many of which are discussed in this book—that apply to all digital systems regardless of their particular form of realisation or application. The other is the availability of electronic logic devices in integrated-circuit form, at a price that, a few years ago, would have been regarded as impossibly low. This low price has enabled digital techniques to be used in systems where previously such methods would have been regarded as quite uneconomic.

#### 1.1 What are digital systems?

All methods of specifying quantities are either continuous or discrete. In the former case, for example, the height of a column of liquid in a tube, all heights are possible between zero and some maximum value limited by the length of the tube. A scale might be used to measure the height of the liquid but the liquid itself will move smoothly between the divisions on the scale and, if measurement could be made sufficiently accurate, an infinity of possible heights would be available. Discrete systems, for example, the mileometer (odometer) used on motor cars, have a limited (although perhaps large) number of possible readings or output values. It is normally impossible to specify the distance travelled by the car to better than the nearest whole mile;

if a 'tenths' digit is provided the resolution of the system is improved but the distance can still be specified only to the nearest tenth of a mile.

In general all systems that fall into the discrete category can be regarded as digital, although certain classes of digital system have a more restricted definition. In electrical terminology continuous systems, as opposed to digital ones, are often referred to as *analogue*. This is because most, if not all, physical variables (for example, temperature, pressure, voltage and current) are continuous quantities and it is often convenient to process a voltage or current that is the analogue of some non-electrical quantity. This technique, analogue computing, has been highly developed and is widely used in specialised applications such as control-system simulation. Computers operating in a discrete mode—digital computers—are used in a much wider range of applications.

#### 1.2 How are digital systems realised?

Any system that can be constrained to have a finite number of levels can be regarded as digital. For example, the discs carrying the figures in the mile-ometer are constrained by mechanical means to have only ten allowed angular positions, as opposed to complete freedom of rotation. The use of ten levels is particularly convenient for systems requiring human involvement. In engineering practice, however, the use of only two levels is particularly attractive. The levels can be widely separated; this allows each level to be severely degraded by deterioration or inadequacy of system components before there is any danger of confusion between the two. For this reason most digital systems operate in a two-level or 'binary' mode, with translation to (or from) ten levels where human intervention is required.

The levels chosen are, very often, merely the presence, or absence, of some physical quantity. In electrical terms this naturally suggests the presence or absence of a voltage (or current); alternatively a circuit, represented by the contacts of a switch or relay, might be 'open' or 'closed'. Hydraulic and pneumatic digital systems are widely used in the control of machinery; here the two levels are represented by the presence or absence of the appropriate pressurised fluid.

Each variable that is permitted to have one of only two possible values is a binary digit (or bit). Digital-system design consists essentially of devising an interconnection of processing elements that produces the desired relationship between an input pattern of bits and the required output pattern. In sequential systems, introduced in chapter 3, the output pattern depends not only on the present input pattern but also on previous ones. In view of the use of only two levels, the number of possibilities when acting on a given number of digits can be unambiguously defined. Details are discussed in chapter 2. The basic principles of design discussed in this book apply regardless of the physical form that the binary variables take. However, purely electronic realisation is

by far the most common and this book is written primarily from this point of view. Electronic logic circuits are now normally, but not always, realised in integrated-circuit form. Integrated circuits consist of the components required for realisation of a series of digital functions produced on a single 'chip' of silicon that is only a few millimetres square.

#### 1.3 Binary representation of quantities

An appropriate code must be used if quantities are to be satisfactorily represented over a wide range using binary digits. Although by no means the only possibility, pure binary code is very widely used. In this code adjacent digits are given values (or weights) that are related by a factor of two, starting with  $2^0$  (=1), just as adjacent digits in decimal numbers are related by a factor of ten. In the decimal system the magnitude of each digit must be specified between zero and nine; in the binary system each digit can be only present (one) or absent (zero). For example, 1101 represents

$$1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 8 + 4 + 0 + 1 = 13$$

By a similar process decimal fractions can be specified as a sum of binary fractions. Note that, because it normally takes a finite time to convert a physical quantity into binary digits, and these digits can change only at a finite rate, digital quantities are discretised not only with respect to magnitude but also with respect to time (that is, they are *sampled*).

Quantities that can be either positive or negative require an additional digit to specify the sign. Although 'sign-and-magnitude' notation is occasionally used, two's complement notation is more common. In this, the magnitude of a negative number is subtracted from  $2^n$  to form the complement, where n is the number of digits in the magnitude part of the number. This approach has the advantage that subtraction may be performed merely by adding the complement of the number to be subtracted.

Although convenient from a processing point of view, pure binary code leads to hardware complexities when a decimal input or display is required. For this reason, systems in which decimal input or output facilities are a significant part of the total system (for example, digital-voltmeters and pocket calculators) often work in a binary-coded decimal (BCD) mode. In this, numbers are represented in decades, but within the decades the ten levels are specified by means of binary code. For example, 0001 0011 1001 represents 139. The price of easy conversion to and from decimal is that more digits are required and some operations, particularly arithmetic, become more complex. Codes having other weightings (for example, 1, 1, 2 and 5) have been used to represent the ten levels within each decade. These are to be avoided since true binary-coded decimal is widely used and any deviation from this can result in incompatible pieces of equipment.

#### 1.4 Serial and parallel data

It is evident from the previous section that transmission of non-trivial numerical information requires several digits. These digits can be transmitted simultaneously (in parallel) or sequentially (serially). The former has the advantage of speed but requires one transmission path for each digit. Serial transmission requires only one path regardless of the number of digits but restricts the speed of transmission by an amount that, for a given transmission system, is proportional to the number of digits. Parallel transmission would normally be used over short distances (perhaps within a system). For economy over longer distances a serial method would normally be used. Parallel-to-serial and serial-to-parallel conversion is readily achieved (see chapter 3).

#### 1.5 Comparison of analogue and digital systems

It could be inferred easily from section 1.1 that analogue systems are potentially more accurate than digital ones, which have a finite resolution. In practice this is not the case; in all natural processes there is an inevitable randomness, generally described as *noise*, which means that the infinitesimal resolution that is theoretically possible can never be realised as a reliable measurement. Quantities represented in digital form, however, can often be interpreted with no loss of accuracy even in the presence of considerable noise; but when the noise exceeds a certain threshold, errors can be very large.

These concepts can be illustrated by means of the elementary examples of section 1.1. Unfavourable conditions such as poor visibility, vibration and an unstable location for the observer would decrease the accuracy with which the height of liquid in the tube could be measured. On the other hand the figures on a series of dials, such as a mileometer, could be read without loss of accuracy under such conditions. However, if the conditions were to become particularly poor, a 6 (for example) could be mistaken for an 8 or a 9 and relatively large errors would occur.

Digital systems operating properly below the critical level of noise will always provide the same results for a given series of inputs. This can give rise to a false sense of confidence since errors due to sampling and discretisation will always be present on the input data that the system processes.

In general, therefore, analogue systems are less precise than digital ones but are often faster since they can operate at their maximum rate without the need for sampling. Historically they have also been regarded as simpler and cheaper. However, the development of complex digital integrated circuits has swung the balance in favour of digital realisation for many applications.

# Review of Combinationallogic Techniques

#### 2.1 Logic levels

Any logic device (or indeed, system) can be viewed as a processing unit. Certain inputs are applied, and certain outputs then appear. These inputs and outputs can take many different forms. For example, they can be voltages, currents, pressure, light, etc., or a mixture of these variables. In the majority of logic devices currently available, the inputs and outputs are voltages. For definiteness, all inputs and outputs in the ensuing discussion will be assumed to be voltages unless stated otherwise.

Having agreed to select voltages to represent inputs and outputs, the next step is to specify how voltage waveforms should be used to convey information. The information of concern is assumed to be a binary digit (bit), which can have only one of two possible values. These values can have various meanings. For example, true, false; on, off; one, zero; 1, 0 are some of the meanings that have been attached to these two values. The voltage waveforms necessary to distinguish between these values could, in principle, be chosen in a great variety of ways. For example, two different sinusoidal frequencies could be used, or two different phases of one frequency (with respect to some reference phase) could be employed. Alternatively, a square wave and a triangular wave could be used, or two rectangular waves with different mark-to-space ratios. The use of two different d.c. levels could also be considered.

The last possibility is very attractive from the design point of view, since it will probably result in a less complicated circuit than the other ideas mentioned. The use of d.c. levels can be related to the well-known switching properties of transistors (which can be manufactured in integrated-circuit form). It is for this reason that the two values of a bit are usually associated with d.c. levels, and are referred to as the logic levels of the bit.

Strictly speaking, the association of a logic level with a d.c. level is not

correct. The logic level in practice must cover a range of d.c. levels. It is necessary to have a range in order to cope with the problems of noise pick-up, varying power supply, ageing of components, etc. In transistor-transistor logic, for example, inputs are allowed in the ranges -1.5 to 0.8 V (logic level zero) and 2.0 to 5.5 V (logic level one). The corresponding output ranges are 0 to 0.4 V and 2.4 to 5.0 V. It is seen that both input ranges are somewhat larger than the corresponding output ranges. The minimum difference in ranges is defined to be the worst-case noise margin for each logic level. For example, logic level one has a worst-case noise margin 2.4-2.0 V = 400 mV. In this case the same noise margin exists for logic level zero.

For both input and output ranges there exists a forbidden band of values. If an input exists in this forbidden band, the output might be anywhere from 0 to 5 V (which includes its forbidden band). Whatever voltage the output assumes, this value could change dramatically if the original device were replaced by another of the same type. For this reason, operation in the forbidden bands is avoided in practice.

There are many textbooks that give detailed design information on logic levels and noise immunity for various logic families. The reader is referred to Motorola (1968, 1973) for more details.

#### 2.2 Gates

The majority of the logic gates that are encountered in practice are of the multiple-input/single-output type. Thus the gate can be considered as an information-combining unit. It accepts several input bits of information and then processes these bits to produce only one output bit. In a sense, information is being destroyed (or entropy increased) in the gate. This entropy point of view has been developed by Matheson (1971a, 1971b).

An important feature of electronic gates is that of unidirectional operation. No matter what signals are impressed on a gate output, the input levels normally remain unaffected. This situation is not true, for example, with relay circuits. With these bilateral circuits, backward paths can occur, which might give rise to incorrect operation.

The simplest way to describe the action of a gate is to prepare an input/output table for the gate. Such a table is conventionally referred to as a *truth table*. This table should show the resulting output for all possible input combinations. Inputs will be denoted by  $x_1, x_2, \ldots, x_n$ , and the output by z. All these variables are binary, and so can assume only the logic levels zero or one as discussed previously.

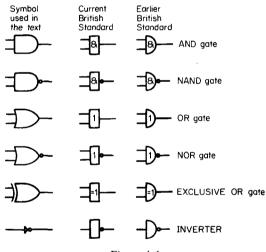

Figure 2.1 Truth table and symbol for a two-input AND gate.

As a first example the truth table of a two-input AND gate will be considered. This truth table is shown in figure 2.1, where logic level *one* is indicated by 1, and logic level *zero* is indicated by 0. Note that all possible input combinations are listed in the table. The symbol for this gate is also shown in figure 2.1. The gate symbols used in this book are in accordance with MIL STD 806 B. It is common practice for manufacturers to use this symbol set. In appendix 1 a list of equivalences is given between these symbols and other widely used equivalents.

The action of this gate can also be described algebraically, as follows

$$z = x_1 x_2$$

In this notation 'multiplication' indicates the AND operation. Letting  $x_1$  and  $x_2$  assume definite values and referring to the truth table of figure 2.1, it is seen that

$$0 \cdot 0 = 0$$

$$0 \cdot 1 = 0$$

$$1 \cdot 0 = 0$$

$$1 \cdot 1 = 1$$

which explains why the AND operator is represented by multiplication. It is obvious that  $z = x_1x_2 = x_2x_1$ , which shows that the AND operation is commutative.

The action of the AND gate can be extended to the *n* inputs  $x_1, x_2, \ldots, x_n$ . Then  $z = x_1 x_2 \ldots x_n$ , which indicates that z = 1 only when all  $x_i = 1$ .

Figure 2.2 Truth table and symbol for a two-input OR gate.

The truth table and symbol for the two-input inclusive OR gate are shown in figure 2.2. Algebraically this truth table is represented as

$$z=x_1+x_2$$

where the plus sign indicates the OR operation. Again, letting  $x_1$  and  $x_2$  assume definite values, the table shows that

$$0+0=0$$

$0+1=1$

$1+0=1$

$1+1=1$

which agrees with our notion of addition (except for the last line). This gate is called inclusive OR because the last line gives z=1 for both  $x_1=1$  and  $x_2=1$ . The operation is again commutative, for  $z=x_1+x_2=x_2+x_1$ . There is

another gate, the exclusive OR gate, which has the property z=1 when either but not both inputs are at *one*. This gate excludes or prevents the output becoming *one* when the two inputs are simultaneously at *one*. The exclusive OR operation is also commutative.

In the inclusive OR gate, let n inputs  $x_1, x_2, \ldots, x_n$  be applied. Then  $z = x_1 + x_2 + \cdots + x_n$ , with the result that z is *one* whenever one or more of the inputs are at *one*.

Some simple rules for the 'addition' and 'multiplication' of logic expressions are now given. Recalling that 1 (or one) stands for 'on' and that 0 (or zero) stands for 'off', it is readily seen that for some logic expression g,  $1 \cdot g = g$ ,  $0 \cdot g = 0$ , 1 + g = 1, 0 + g = g. It also turns out that (e + f)(g + h) = eg + eh + fg + fh, as is the case for algebraic multiplication. With a combination of these rules, various results can be obtained. For example,  $(x + g)(x + h) = xx + xh + xg + gh = x + x(g + h) + gh = x(1 + g + h) + gh = x \cdot 1 + gh = x + gh$ . Rather than develop a long list of such specialised formulae, it is quite often easier to work directly with Karnaugh maps, as will be seen subsequently.

Returning to the discussion of gates, the simplest gate of all is the inverter of figure 2.3. This gate can be represented by a circle or a triangle followed by

$$\begin{array}{c|c} x & z \\ \hline 0 & 1 \\ 1 & 0 \end{array}$$

Figure 2.3 Truth table and symbol for an inverter gate.

a circle, and has the property of complementing (or loosely, 'inverting') the input. The output is often indicated by  $\bar{x}$ , where the bar indicates the complement (or logical inverse) of x. The definition of a logical inverse is that  $x + \bar{x} = 1$ . From the truth table, it is readily seen that  $x\bar{x} = 0$  and  $(\bar{x}) = x$ .

The first equation will be central to the Karnaugh map, which is discussed in section 2.3. The last equation will prove to be extremely useful for logic-circuit transformation. In words, this equation states that two (or any even number, for that matter) inverters in series cancel each other out. Conversely, it is possible to 'grow' two inverters on a connection wire without disturbing the operation of a logic circuit.

The inverter can be combined with the AND- and OR-gate outputs to create the NAND and NOR gates, respectively. The N indicates that the output is negated (that is, inverted). The symbols and truth tables for these gates are shown in figure 2.4. In this figure it is seen that if  $x_1 = x_2$  both of these gates reduce to inverters.

Figure 2.4 Symbols and truth table for two-input NAND and NOR gates.

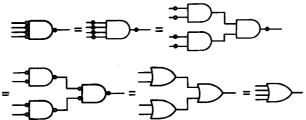

Inverters can also be added to the inputs of a gate. Consider what happens when inverters are added to the inputs of the gates of figure 2.4. By referring to the truth tables of this figure, it can be seen that the equivalences of figure 2.5 hold. For example, the inputs  $x_1 = 0$ ,  $x_2 = 0$  become inverted  $(\bar{x}_1 = 1, \bar{x}_2 = 1)$ , which results in z = 0 for both cases in figure 2.4. Other input combinations can be checked in a similar manner. Whenever one of the symbols of figure 2.5 appears in a logic circuit, it can be immediately replaced by its equivalent, if desired.

Figure 2.5 Gate equivalences.

These results can be used to produce a number of equivalent circuits by using a simple pictorial technique. The method is best illustrated by example.

#### Example 2.1

Find equivalent circuits for the NAND and NOR gates of figure 2.4.

Solution Double inverters are grown on each input lead. The equivalences of figure 2.5 are then used. The process is shown pictorially in figure 2.6.

Figure 2.6 Pictorial solution for example 2.1.

#### Example 2.2

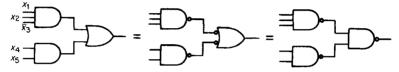

Extend the first equivalence of figure 2.5 to a four-input gate.

Solution The steps of figure 2.7 are used to develop the solution. In this

Figure 2.7 Pictorial solution for example 2.2.

figure it is understood that, if an inverter is adjacent to a gate, it is formed electronically within the gate itself. If the inverter is elsewhere on a connection wire, it represents a separate electronic entity or, possibly, a hypothetical inverter. This solution can be extended to any number of input leads. A similar result can be obtained for the second equivalence of figure 2.5.

#### Example 2.3

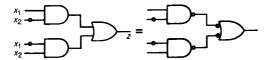

Realise the function  $z = x_1x_2\bar{x}_3 + x_4x_5$  by using NAND gates.

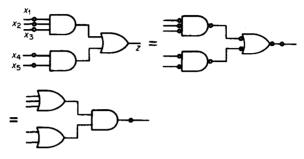

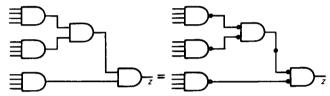

Solution The first step is to draw a logic circuit (called a prototype circuit) which corresponds directly to the algebraic equation for z. The prototype circuit for this example is shown leftmost in figure 2.8. The next step is to grow

Figure 2.8 Equivalent-circuit solutions for example 2.3.

double inverters in such a way that all the gates become NAND gates. From example 2.1 it was found that a NAND gate can be formed either by adding an inverter to the output of an AND gate, or by adding inverters to the inputs of an OR gate. This step is performed in the middle circuit of figure 2.8. In fact, this circuit is the solution to the problem. Many designers prefer not to have two different symbols for a NAND gate on the same diagram, however, and so will convert the middle circuit to the rightmost one. It is a matter of taste as to which representation is preferred. If the input  $\bar{x}_3$  is not available, an additional NAND gate (with all its inputs tied together) will be necessary for the inversion of  $x_3$ .

The last example illustrated that a prototype circuit consisting of AND and OR gates can be converted to one using only NAND gates. This principle can be extended to *any* prototype circuit consisting of AND, OR, NAND and NOR gates. This prototype circuit can always be transformed into a NAND-gate-only circuit by the inverter-growing process (with discrete inverters provided by degenerate NANDs). This argument can be applied also to the transformation of any prototype circuit to a NOR-gate-only circuit.

The usual transformation problem is to produce an equivalent circuit with as few *discrete* inverters as possible. In a processing sense, discrete inverters are redundant—they neither generate nor destroy information. Usually some trial and error is necessary in order to minimise discrete inverters, as illustrated in the following example.

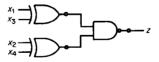

#### Example 2.4

Realise the exclusive OR function  $z = x_1 \bar{x}_2 + \bar{x}_1 x_2$  with two-input NAND

gates using as few gates as possible. The complemented variables  $\bar{x}_1$  and  $\bar{x}_2$  are not available elsewhere and so must be generated as part of the solution.

Solution The direct algebraic realisation of z and its subsequent transformation is shown in figure 2.9. Five gates are required, with two of the gates

Figure 2.9 Direct realisation of example 2.4.

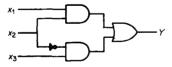

acting as inverters. In searching for a simpler solution, a promising idea would be to use one gate to produce  $\bar{x}_1 + \bar{x}_2$  (a NAND gate is equivalent to an OR gate with inverters on the input). The gate is then 'more active' than it would be with both of its inputs connected together. This output, when ANDed with  $x_1$ , produces  $x_1\bar{x}_2$  (since  $x_1\bar{x}_1=0$ ), which is one of the desired output terms. The rest of the design is straightforward, and is shown in figure 2.10. It is seen that this indirect realisation uses only four gates, and so represents an improved solution.

Figure 2.10 Another solution for example 2.4.

In attempting to minimise discrete inverters it is generally necessary to use a variety of gate types. For example, sometimes a mixture of NAND and NOR gates will completely eliminate the need for discrete inverters. Also, as a rule it is desirable to use one many-input gate rather than several small ones in minimising the number of gates (and connection wires) needed in the realisation. But in a manufacturing environment it is usually beneficial to reduce the number of gate types to a minimum. This procedure eases stocking problems and assembly procedures. There can also be significant price differences between different gates. Therefore, for example, a company might decide to use only two- and four-input NAND gates. Such a policy will usually result in some of the gates being used as simple inverters. This result is not necessarily bad, however. In the implementation of a large system there will usually be some gates left over. These extra gates can then be put to use as inverters. Other criteria can also be used to estimate whether or not a design is optimal. Some of these criteria are discussed in section 5.5.

Occasionally a logic-circuit design requires numerous inverters for the  $x_i$  inputs. A general method for dealing with this case will be illustrated with the following example.

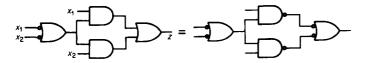

#### Example 2.5

Realise the function  $z = \bar{x}_1 \bar{x}_2 \bar{x}_3 + \bar{x}_4 \bar{x}_5$  with AND gates, OR gates and inverters, using as few inverters as possible. The complemented inputs  $\bar{x}_1$  are not available and so must be generated within the circuit.

Solution The transformations of figure 2.11 are used, which result in the saving of four discrete inverters.

Figure 2.11 Discrete-inverter reduction for example 2.5.

The last example led to the equivalence

$$z = \bar{x}_1 \bar{x}_2 \bar{x}_3 + \bar{x}_4 \bar{x}_5 = (x_1 + x_2 + x_3)(x_4 + x_5)$$

where the long bar indicates inversion (or complementation) of the ANDed output. This equation is a particular example of De Morgan's theorem. In algebraic form this theorem gives an equivalence between two logic expressions, for which one expression contains complements of all terms and operations of the other expression. It can be written as

$$z = \sum_{i} P_{i}$$

$$\bar{z} = \prod_{i} \bar{P}_{i}$$

where each  $P_i$  is the product (or ANDing together) of input variables (or their complements). For example, let  $P_1 = x_1x_2$  and  $P_2 = \bar{x}_1x_3$ . Then  $\bar{z} = (x_1x_2)(\bar{x}_1x_3) = (\bar{x}_1 + \bar{x}_2)(x_1 + \bar{x}_3)$ . The natural way to apply De Morgan's theorem for inverter reduction, however, is to use the pictorial procedure of the previous example. This procedure tends to produce fewer errors than pure algebraic manipulation based on De Morgan's theorem.

#### 2.3 The Karnaugh map

The discussion so far has been concerned with gates and the realisation of some output specifications in gate form. Attention is now focused on the minimisation of the specification itself.

#### 2.3.1 Expansion into minterms

The first task is to develop a method that will detect whether two logical expressions are equivalent to each other. For example, the expressions  $z_1 = \bar{x}_1\bar{x}_3 + x_2x_3 + x_1x_2\bar{x}_3$  and  $z_2 = x_2 + \bar{x}_1\bar{x}_2\bar{x}_3$  are equivalent to each other, but this fact is not obvious from casual inspection of  $z_1$  and  $z_2$ . Looking at  $z_1$  and  $z_2$  more closely, it is seen in each case that there are product terms with one or more input variables missing. These missing variables can be recovered by using the fact that  $x_i + \bar{x}_i = 1$ . Thus,  $z_1$  becomes

$$z_1 = \bar{x}_1 \bar{x}_3 (x_2 + \bar{x}_2) + x_2 x_3 (x_1 + \bar{x}_1) + x_1 x_2 \bar{x}_3$$

=  $\bar{x}_1 x_2 \bar{x}_3 + \bar{x}_1 \bar{x}_2 \bar{x}_3 + x_1 x_2 x_3 + \bar{x}_1 x_2 x_3 + x_1 x_2 \bar{x}_3$

Applying the method to  $z_2$ , it is found that

$$\begin{split} z_2 &= x_2 (x_1 + \bar{x}_1)(x_3 + \bar{x}_3) + \bar{x}_1 \bar{x}_2 \bar{x}_3 \\ &= (x_1 x_2 + \bar{x}_1 x_2)(x_3 + \bar{x}_3) + \bar{x}_1 \bar{x}_2 \bar{x}_3 \\ &= x_1 x_2 x_3 + x_1 x_2 \bar{x}_3 + \bar{x}_1 x_2 x_3 + \bar{x}_1 x_2 \bar{x}_3 + \bar{x}_1 \bar{x}_2 \bar{x}_3 \\ &= z_1 \end{split}$$

This expansion appears to be a retrograde step, since simplification of the output expression was the original intention. None the less, the expansion does provide a standard form for any output expression (which can be used for equivalence checking). This form contains the sum of a number of product terms, each of which contains all the  $x_i$  variables. Such a term is referred to as a minterm. Two output expressions are said to be the same if each contains the same set of minterms. Once an expression has been put into minterm form, the next task is to find the simplest expression that represents the set of minterms.

#### 2.3.2 Development of the map

Referring to the above example, it is seen that each time a term is multiplied by  $(x_i + \bar{x}_i)$ , the number of terms increases by one, and each term contains one more variable. Both effects increase the number of gates required in the realisation. Conversely, if two terms can be found that are the same except for a single variable, say  $f_1x_i + f_1\bar{x}_i$ , then these expressions can be combined and the  $x_i$  variable eliminated. This procedure is the basis of the Karnaugh-map method.

The Karnaugh map is composed of squares such that each square represents one minterm. An output expression is entered into a Karnaugh map by simply placing 1's in the appropriate minterm squares. A key feature of the map is that minterm squares that differ in only one variable (for example,  $x_1x_2x_3$  and  $x_1x_2\bar{x}_3$ ) are made to lie next to each other. The eye can then spot clusters of 1's which are essential for map simplification. The main problem in the development of a multivariable map is to provide all the adjacencies that

are needed while confined to two-dimensional space (for ease of working).

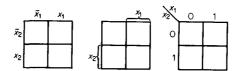

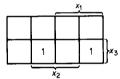

The two-variable map is simple to draw. It is shown in figure 2.12, with three different labelling schemes. The leftmost scheme is the most direct way to indicate minterms. Each minterm is simply the product of a row and a column variable or, in set-theory terms, the intersection of a row strip and column strip. Usually the complemented variables are not labelled, as shown in the centre map. The binary notation scheme is shown at the right. The 0

Figure 2.12 Different forms of a two-variable Karnaugh map.

indicates  $\bar{x}_i$ , while the 1 indicates  $x_i$ . In figure 2.12, the adjacency between minterms is satisfied. The minterm squares  $\bar{x}_1\bar{x}_2$  and  $x_1x_2$  differ by more than one variable change, and so are not considered adjacent (even though their corners touch).

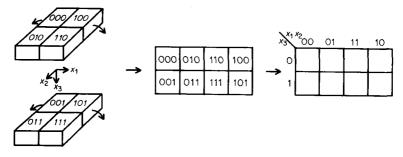

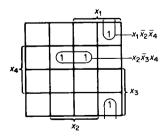

The three-variable map is considered next. In order to meet the adjacency requirements, the natural way to draw this map would be in three-dimensional space. Such a map is drawn at the left in figure 2.13. On this map the  $x_1$  axis is from left to right. Thus the  $x_1$  variable on each block must change from

Figure 2.13 Development of a three-variable Karnaugh map.

0 to 1 in moving from a left-side block to a right-side block. The same arrangement exists for the other two dimensions. However, it is preferable to represent this map in two-dimensional space. This step can be performed by shifting the blocks 000, 100, 001 and 101 in the figure to the front row. Thus, block 000 is put to the left of 010, and so forth. The shifted block pattern is then viewed from the front, which gives the arrangement in the centre of figure 2.13. This rectangle can be labelled with variables, as shown at the right in the figure. The result is a three-variable Karnaugh map, drawn in two-dimensional space. In order to draw this map, it has been necessary to separate 000 from 100 and 001 from 101. These adjacencies can be retained by imagining the map to be joined together at the left and right edges.

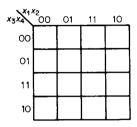

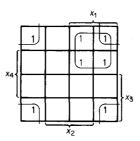

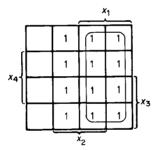

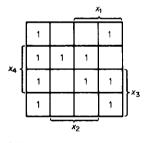

In the construction of a four-variable map the sequence of values for  $x_1x_2$  in figure 2.13 can be repeated along a vertical axis. The result is shown in figure 2.14. In this figure the top and bottom edges are also considered to be adjacent.

Figure 2.14 A four-variable Karnaugh map.

#### 2.3.3 Map entries

When an output expression is given in minterm form the map is readily constructed, by placing 1's in every square that corresponds to a minterm. For example, in the expression  $z = \bar{x}_1 x_2 x_3 + x_1 \bar{x}_2 x_3$ , the Karnaugh-map entries are shown in figure 2.15. In this map it is apparent that the minterms are not adjacent. Each blank square can be given a 0 entry if desired.

Figure 2.15 Entries on a three-variable map for  $z = \bar{x}_1 x_2 x_3 + x_1 \bar{x}_2 x_3$ .

If the output is not given in minterm form, then the map entries will appear in clusters. For example, let  $z = x_2 \bar{x}_3 x_4 + x_1 \bar{x}_2 \bar{x}_4$ . Evidently a four-variable map is required. The first term does not contain  $x_1$ ; therefore, 1's must occur on the Karnaugh map in both the  $x_1$  and  $\bar{x}_1$  regions for this term. A similar result holds for the  $x_3$  variable in the second term. The resulting map for this expression is shown in figure 2.16. Loops have been placed around the 1's

Figure 2.16 Map entries for  $z = x_2 \bar{x}_3 x_4 + x_1 \bar{x}_2 \bar{x}_4$ .

common to each term of z. Note that the 1's in the rightmost column are adjacent since the top and bottom edges of the map are imagined to touch each other. In this example each term with one missing variable gives rise to two 1's on the map.

The next example of interest is  $z = \bar{x}_2\bar{x}_4 + x_1\bar{x}_3$ . The first term gives rise to 1's in all the corners (which are imagined to be adjacent) and the second term gives a square cluster of four 1's in the upper right corner, as shown in figure 2.17. Note in this example that minterm  $(x_1\bar{x}_2\bar{x}_3\bar{x}_4)$  is included in more than one term. In general, if a term has k missing input variables, the map will have

Figure 2.17 Map entries for  $z = \bar{x}_2 \bar{x}_4 + x_1 \bar{x}_3$ .

a cluster of  $2^k$  adjacent 1's. The cluster will be rectangular in form with each side of the rectangle having a number of squares that is a power of two. For example,  $1 \times 1$ ,  $2 \times 2$  and  $2 \times 4$  are permitted, but  $2 \times 3$ ,  $1 \times 6$  or  $2 \times 6$  are not.

#### 2.3.4 Map factoring

The process of map factoring involves the grouping of the 1's on a map into rectangles such that the rectangles are as large as possible and such that all 1's are covered at least once. When this has been accomplished the output z can be read from the map in its simplest form. Each rectangle is said to represent a factor of the map. This process is the reverse of expanding z into minterm form. In general a rectangle of 1's is called an *implicant* of z. If the rectangle has been made as large as possible (maximum area) it is referred to as a prime implicant. If a minterm cell is contained in only one prime implicant, that prime implicant must appear in the output expression. Such an implicant is called an essential prime implicant. These terms will be illustrated by the example  $z = \bar{x}_1 x_2 \bar{x}_3 + x_1 x_2 \bar{x}_3 + x_1 \bar{x}_2 \bar{x}_3 + x_1 \bar{x}_2 x_3$ , which is shown in the map of figure 2.18. The implicants are the original minterms together with the

Figure 2.18 Illustration of implicants, prime implicants, and essential prime implicants.

terms  $x_2\bar{x}_3, x_1\bar{x}_3$  and  $x_1\bar{x}_2$ . The prime implicants are  $x_2\bar{x}_3, x_1\bar{x}_3$  and  $x_1\bar{x}_2$ . The essential prime implicants are  $x_2\bar{x}_3$  and  $x_1\bar{x}_2$ . These two implicants include (or cover) all the 1's on the map, with only two factors. The third (redundant) prime implicant  $x_1\bar{x}_3$  is not needed in the generation of z.

In general, map factoring consists of finding the prime implicants on a map, and then selecting the minimal (irredundant) set of prime implicants. These two steps are often done simultaneously in map factoring, especially if the number of variables is small. The 'method of attack' is first to factor the 1's that can be combined in only one way. The resulting prime implicants will be essential. The remaining 1's are then factored. In figure 2.18, for example, the 1's representing  $\bar{x}_1x_2\bar{x}_3$  and  $x_1\bar{x}_2x_3$  can only be combined in one way  $(x_2\bar{x}_3$  and  $x_1\bar{x}_2)$  and so these are essential prime implicants. In this case these essential prime implicants cover all the 1's, and so the map has been completely factored. It would be a mistake to include the implicant  $x_1\bar{x}_3$  in z, even though it is the first rectangle spotted on the map.

Referring to figure 2.17 it is seen that 1's can be re-used if necessary in factoring. The goal should always be to make the rectangle as large as possible, regardless of how often 1's are re-used. To illustrate this point, consider the map of figure 2.19. How shall the remaining 1's be factored? If

Figure 2.19 An example of 1's re-use.

they are lumped together the resulting implicant is  $\bar{x}_1x_2$ . But this implicant is not prime. The corresponding prime implicant  $x_2$  will include the column  $x_1x_2$ , which has already been used in the other prime implicant.

#### 2.3.5 Many-variable maps

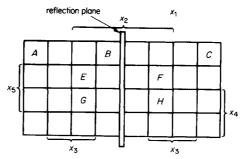

The Karnaugh map can easily be extended to handle five and six input variables. The five-variable map is shown in figure 2.20. In the middle of the map is a reflection plane, which can be likened to a mirror. In this map minterm A is not only adjacent to B, but is also adjacent to C (by the action of the mirror). Minterms E, F, G and H are all adjacent and thus form a (prime) implicant square.

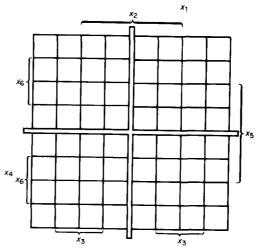

A reflection plane can be added to the vertical direction, which leads to a six-variable map, as shown in figure 2.21. The figure has sixty-four minterm squares. The number of adjacencies is considerable, and it requires some

Figure 2.20 A five-variable Karnaugh map.

practice to factor the map in an optimal manner. None the less, the aforementioned principles are applicable here.

Figure 2.21 A six-variable Karnaugh map.

A seven-variable map can be constructed by placing two six-variable maps side by side. An eight-variable map requires four six-variable maps arranged in a square. These higher-order maps are of most use for the case where the number of minterms is reasonably small, and yet large enough for some factorisation to occur. If more than eight input variables are present, the authors have found that it will be necessary either to partition the problem (which is discussed in section 2.4) or to employ computer programs. Examples of such computer programs can be found in Dietmeyer (1971). A comprehensive bibliography of books on logic design is given by Lewin (1968). Finally Potton (1973) gives an expanded treatment of Karnaugh maps and combinational logic.

#### 2.3.6 Selection of required prime implicants

The removal of obvious essential prime implicants (in which a 1 can only be

combined in one way) has already been discussed. The next problem is to determine which of the remaining prime implicants are to be used.

In general a table can be formed with minterms across the top row and prime implicants down the left-hand side. Such a table is shown in figure 2.22.

|            | required minterms |       |       |       |       |

|------------|-------------------|-------|-------|-------|-------|

|            |                   | $m_1$ | $m_2$ | $m_3$ | $m_4$ |

| prime      | A                 | 1     | 1     |       | 1     |

| implicants | В                 | 1     | 1     | 1     |       |

| •          | $\boldsymbol{C}$  |       |       | 1     | 1     |

Figure 2.22 Table used in the selection of essential prime implicants.

The essential prime implicants can be detected by looking for columns with only a single 1. After these implicants and their associated minterms are removed, it is not immediately obvious which combination of remaining prime implicants will provide cover of the remaining minterms.

An algebraic expression of the complete coverage can be written as follows. Minterm  $m_1$  requires A, minterm  $m_2$  requires A+B, and so on. To satisfy all minterms, A(A+B)(B+C)(A+C) is required. This expression can be expanded into  $(AA+AB)(AB+BC+AC+CC)=(A+AB)\cdot(AB+AC+BC+C)=(A+AB)\cdot(AB+AC+BC+C)=(A(1+B))(AB+C(A+B+1))=A(AB+C)=AB+AC$ , since (x+1)=1. The result is that either A and B or A and C can be the required prime implicants. The choice between these two sets is arbitrary. It could well depend on the ease of implementation in relation to other prime implicants. The above procedure was first described by Petrick (1959) and is sometimes referred to as Petrick's method.

The Karnaugh map can be used in this expansion as well. Let  $z = A(A+B) \cdot (B+C)(A+C)$ . By using De Morgan's theorem (see section 2.2) it is found that  $\overline{z} = \overline{A} + \overline{AB} + \overline{BC} + \overline{AC}$ . These terms are entered on a three-variable map as shown in figure 2.23. The remaining squares are then given a 0 entry. These

Figure 2.23 Karnaugh map for the selection of essential prime implicants.

zeros represent the factors of the complement of  $\bar{z}$ , that is, the factors of z. Factoring the zeros gives z = AB + AC, which is the result of the algebraic expansion above.

Either of these techniques gives all combinations of prime implicants that

are necessary and sufficient to provide complete coverage.

#### 2.3.7 Don't cares

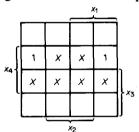

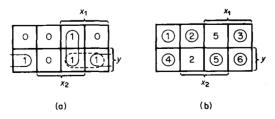

In some designs it is known that one or more input patterns will never occur. If the input is coming from a four-bit decade counter (counting from 0 to 9), for example, it is known that the bit patterns corresponding to the numbers from 10 to 15 should never occur. These unused patterns are commonly referred to as don't care conditions. The corresponding minterm squares in the Karnaugh map are marked with  $\times$ 's to indicate the don't cares. When factoring the map, these don't cares can be used, if desired, for forming larger prime implicants. For example, figure 2.24 shows the map for which z=1 whenever

Figure 2.24 Example of don't cares.

the count exceeds 7. If the don't cares are not used, then  $z = \bar{x}_2 \bar{x}_3 x_4$ . If they are used, however,  $z = x_4$ . Before minimising a logic expression it is obviously desirable to learn of all the don't cares that will exist in practice. Sometimes it is also desirable to find a minimal expression for all the don't cares. In the unlikely event that one should occur (due to circuit mal-operation), an alarm can be produced. In the above example the don't care alarm would be  $z = x_2 x_4 + x_3 x_4$ . Sometimes it is desirable to factor the 0's (or blanks) rather than the 1's. The x's can also be used to simplify this factoring.

#### 2.4 Partitioning

Combinational-logic designs that contain a large number of input variables are occasionally encountered. An attempt to minimise the resulting expressions directly, even with computer programs, can be quite time-consuming and error-prone. An examination of the over-all design requirement will often reveal an inner structure, or partitioning, of the problem. Each block in the partitioning will represent a simplified logic design. This breaking-up of a massive circuit into smaller blocks is useful not only from a design point of view but also for subsequent tasks, such as a description of circuit functions in a manual, and for mal-operation detection. This partitioning is a reflection of man's desire to break up any complex function into block-diagram form, where each block is readily understood. An example at this point will prove instructive.

#### Example 2.6

Design a two-bit equality detector for the words  $x_1x_2$  and  $x_3x_4$ . The output z is *one* only if the corresponding bits in each word are equal. The circuit is to be made with two-input NAND gates.

Solution If a direct solution is attempted, then the first step is to write a complete expression for z, which is  $z = \bar{x}_1 \bar{x}_2 \bar{x}_3 \bar{x}_4 + \bar{x}_1 x_2 \bar{x}_3 x_4 + x_1 \bar{x}_2 x_3 \bar{x}_4 + x_1 x_2 x_3 x_4$ . If this expression is put on a four-variable Karnaugh map, it will be seen that no factoring is possible. A direct realisation of z requires fifteen two-input NAND gates plus an additional fourteen NAND gates used as inverters.

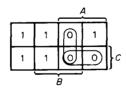

In seeking a partition for this design, it is worth while to consider the design objective again. On reflection, it is seen that the objective can be met with a single-bit equality block and a block that combines or processes these equalities. The design has therefore been simplified. The design of the single-bit equality block is straightforward. It is specified by the truth table and given by the circuit in figure 2.25. This circuit is the exclusive OR gate of example 2.3,

Figure 2.25 Single-bit equality detector for example 2.6.

with an inverter on the output. The equality-combining block for this example is simply a two-input AND gate. The complete realisation is given in figure 2.26. It requires nine NAND gates plus three NAND gates used as inverters.

Figure 2.26 Two-bit equality detector in partitioned form.

In general it is not known whether a partitioned design will require greater or fewer gates than an unpartitioned one. However, if the partitioned design requires more gates, these extra gates can often be justified by ease of design, ease of understanding and ease of testing. The partitioned design is also readily expandable to handle more digits than the original specification.

#### 2.5 Iterative circuits

The central idea of an iterative design is to perform a partitioning such that all blocks are *the same*, with the possible exception of the first and last blocks. Iterative designs are usually restricted to specifications that contain a great deal of symmetry. An example should clarify these points.

#### Example 2.7

Design a circuit for the twenty input variables  $x_1, x_2, \ldots, x_{20}$  such that z is one whenever exactly one of the inputs is at one.

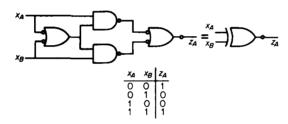

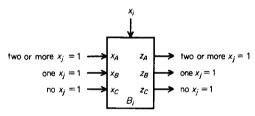

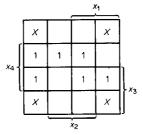

Solution It is clear that a direct approach would result in a massive combinational circuit. In solving this example, it is first imagined that a partitioning block  $B_i$  somewhere in the centre of the circuit will have as inputs  $x_i$  and the outputs of the previous block  $B_{i-1}$ . A list of relevant input and output lines for  $B_i$  is formed, such that the output lines are related to the input lines except for the  $x_i$  itself. The list for the present example is shown in figure 2.27. It is

Figure 2.27 A list of input and output lines for the iterative block  $B_i$  in example 2.7.

seen that a four-input three-output circuit is necessary. In principle a truth table can be produced for each z, and the expression minimised on a Karnaugh map. In this case the necessary expressions can be written down by inspection, as follows

$$z_{A} = x_{A} + x_{B}x_{i}$$

$$z_{B} = x_{B}\bar{x}_{i} + x_{C}x_{i}$$

$$z_{C} = x_{C}\bar{x}_{i}$$

These expressions are easily realised in gate form. Attention must now be paid to the first and possibly last blocks. The first block will reduce to

$$z_A = 0$$

$$z_B = x_1$$

$$z_C = \bar{x}_1$$

(since there are no previous x inputs). The last block can be designed to produce the required output z, which results in the design equation

$$z = x_B \bar{x}_{20} + x_C x_{20}$$

Sometimes it is necessary to treat the first few blocks as special cases. For example, if the requirement for z involves three inputs, blocks  $B_1$  and  $B_2$  will be preliminary stages, having different structures from the iterative block.

The above example illustrates the simplicity of iterative design compared to straightforward design. All of the advantages of partitioning referred to in section 2.3 are enjoyed in an iterative design. A further advantage is that additional blocks can easily be added (or subtracted) if it is decided to change the number of variables at some later stage. One disadvantage is that a change in  $x_1$ , for example, will have to 'ripple' through the entire circuit before changing z. If a large number of blocks is being used, the resulting delay could be significant.

#### 2.6 Multiple outputs

In the previous section an iterative design that required three outputs was given. A straightforward realisation of these outputs would involve treating each output variable as independent of the other outputs, the result being a separate map factoring for each output variable. Each z would be only a function of the  $x_i$ , and not a function of intermediate outputs of the other z circuits.

The advantages of this procedure are ease of design, ease of circuit understanding and ease of troubleshooting. For example, each z circuit could be put on a separate plug-in card. Repair in this case reduces to card replacement. The disadvantage of the procedure is that more gates are usually required.

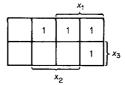

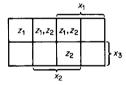

The use of common map factors to reduce the number of gates is best illustrated through some examples. In figure 2.28 a three-variable map with

Figure 2.28 Example of multiple-output simplification.

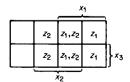

the two outputs  $z_1$  and  $z_2$  is shown. It is seen that both  $z_1$  and  $z_2$  require the prime implicant  $x_2\bar{x}_3$ . This factor can therefore be used in the formation of  $z_1 = x_2\bar{x}_3 + \bar{x}_1\bar{x}_3$  and  $z_2 = x_2\bar{x}_3 + x_1x_2$ , which will reduce the gate count. As a counter example, however, consider the map of figure 2.29. The common area

Figure 2.29 Counter-example of multiple-output simplification.

$x_1x_2$  is *not* a prime implicant of either output. In fact the prime implicant of  $z_1$  (that is,  $x_1$ ) overlaps with the prime implicant  $x_2$  of  $z_2$  to produce the common area. In this case the simplest outputs are  $z_1 = x_1$ ,  $z_2 = x_2$ , and not  $z_1 = x_1x_2 + x_1$ ,  $z_2 = x_1x_2 + x_2$ .

In general, the use of common factors to simplify multiple-output expressions works best for factors that are common *prime* implicants to two or more outputs. If the common factor is an obvious essential prime implicant to the outputs, so much the better. Usually some trial and error is necessary to see if a real advantage is gained in using common factors for multiple-output circuits. A formal technique for the common-factors approach is given in Hill and Peterson (1968).

#### 2.7 Concluding remarks

In using logic gates a number of practical points should be kept in mind. First of all there is the loading problem. The output of a gate is simply not able to drive an unlimited number of gate inputs. The maximum 'fan-out' (or number of inputs that can be driven) should be established for each family of logic devices (or, in some cases, for each device). The fan-out will represent an upper bound. In some cases it could be necessary to add additional buffer stages to cope with a large fan-out requirement.

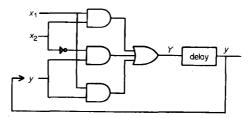

The transient problem should also be considered. In the event of sudden changes in all the inputs to a combinational circuit, brief pulses can appear at the output before the output settles down. These pulses are due to the multipath nature of a combinational circuit, where each path will have a different propagation time. Sometimes these pulses are difficult to see on an oscilloscope, but their presence can be ascertained by their ability to trigger a flipflop, for example. If these pulses are objectionable, they should be filtered out. The simplest way to accomplish this is by the addition of a small capacitance to the output. More will be said about these transient pulses in chapter 4.

When the output of a logic gate switches from one logic level to the other, there is usually a sudden change in the power-supply current to the gate. This transient, if not controlled, can induce false inputs into other gates for a brief period of time. The popular solution to this problem is to provide many power-supply-decoupling capacitors throughout the circuit. These capacitors may be thought of as small batteries that are able to supply sudden, limited current pulses without much voltage variation. Large electrolytic capacitors should not be used for this purpose, since their inputs can be inductive at high frequencies. These capacitors can be used, however, to reduce substantially any mains interference that might exist.

#### 2.8 Examples

This section contains several examples, both worked and unworked, that illustrate many of the salient points of this chapter. The unworked examples

should be capable of solution by readers who have followed the chapter material and the worked examples.

#### Example 2.8

Realise a twelve-input AND gate by using only two- and four-input NAND gates and two-input NOR gates. The realisation should have as few gates as possible.

Solution The first step is the construction of a prototype circuit. In this circuit only two- and four-input gates should be used. To provide rapid concentration, four-input gates will be used for all inputs, as shown in figure 2.30.

Figure 2.30 Prototype and final circuit for example 2.8.

The outputs of these gates can then be combined with two-input gates, or with another four-input gate. (The two-input gates are used in figure 2.30.) The addition of inverters must start at the outputs of the four-input gates, as these gates are to be NANDs. The procedure is then automatic, and yields the circuit on the right in figure 2.30. One discrete inverter is required.

#### Example 2.9

Find all of the prime implicants in the map in figure 2.31.

Figure 2.31 Karnaugh map for example 2.9.

Solution It is tempting immediately to start drawing rectangles around groupings of 1's. This procedure would undoubtedly locate most of the prime implicants, but the problem statement indicates that all of these implicants are to be found. A more systematic procedure is to go to the first square, identify all prime implicants associated with that square, then go to the second square, and so on. The path through the squares will be arranged to cor-

respond to the way that one reads a page—left to right, top row to bottom row. The result of this procedure is as follows.

| •              |           | • •      | •              |          | • • • • • • • • • • • • • • • • • • • • |

|----------------|-----------|----------|----------------|----------|-----------------------------------------|

| minterm square | prime imr | blicants | minterm square | prime in | nnlicants                               |

|                |           |          |                |          |                                         |

| $\bar{x}_1 \bar{x}_2 \bar{x}_3 \bar{x}_4$          | $\bar{x}_2\bar{x}_4, \bar{x}_1\bar{x}_2$    | $\bar{x}_1\bar{x}_2x_3x_4$       | $\bar{x}_1\bar{x}_2, \bar{x}_2x_3x_4$         |

|----------------------------------------------------|---------------------------------------------|----------------------------------|-----------------------------------------------|

| $x_1 \overline{x}_2 \overline{x}_3 \overline{x}_4$ | $\bar{X}_2\bar{X}_4$                        | $x_1 x_2 x_3 x_4$                | $x_1 x_2 x_4, x_1 x_3 x_4$                    |

| $\bar{x}_1\bar{x}_2\bar{x}_3x_4$                   | $\bar{x}_1\bar{x}_2, \bar{x}_1\bar{x}_3x_4$ | $x_1 \bar{x}_2 x_3 x_4$          | $x_1x_3x_4, \bar{x}_2x_3x_4, x_1\bar{x}_2x_3$ |

| $\bar{x}_1 x_2 \bar{x}_3 x_4$                      | $\bar{x}_1\bar{x}_3x_4, x_2\bar{x}_3x_4$    | $\bar{x}_1\bar{x}_2x_3\bar{x}_4$ | $\bar{x}_1\bar{x}_2, \bar{x}_2\bar{x}_4$      |

| $x_1x_2\bar{x}_3x_4$                               | $x_2\bar{x}_3x_4, x_1x_2x_4$                | $x_1\bar{x}_2x_3\bar{x}_4$       | $\bar{x}_2\bar{x}_4, x_1\bar{x}_2x_3$         |

It is therefore found that eight prime implicants exist.

#### Example 2.10

Find a minimal set of prime implicants for example 2.9.

Solution Referring to figure 2.31, the right-side upper corner indicates that  $\bar{x}_2\bar{x}_4$  is an essential prime implicant, as only one combination pattern exists for this square. Removal of this prime implicant leads to the map of figure 2.32, in which the removed 1's are represented as don't cares, since these

Figure 2.32 Removal of an essential prime implicant.

squares can be used again if needed. Forty per cent of the 1's have now been removed! By inspection of the figure it is seen that a minimum of three rectangles (or prime implicants) will be necessary to include all the remaining 1's. One such set is  $\bar{x}_1\bar{x}_3x_4$ ,  $x_1x_2x_4$ ,  $\bar{x}_2x_3x_4$ , and another is  $\bar{x}_1\bar{x}_2$ ,  $x_2\bar{x}_3x_4$ ,  $x_1x_3x_4$ . The second set is simpler and thus represents the 'best' solution. In this example the power of the Karnaugh map as a pictorial display is clearly seen. The map enables man, with his pattern-recognition abilities, to spot the solution (almost) at a glance. The tabular approach—of listing all minterms and prime implicants and then deciding which prime implicants are essential—would be very time-consuming, even for this four-variable problem.

#### Example 2.11

A long corridor is illuminated by thirty light bulbs having a uniform spacing. By each bulb is a phototransistor that is capable of producing a logic output  $x_i$ . If  $x_i$  is zero, the *i*th light bulb is lit. If a bulb failure occurs,  $x_i$  goes to one. For economy, it has been decided that bulbs will be renewed only when three consecutive bulbs have failed. Design a logic circuit that will detect this condition.

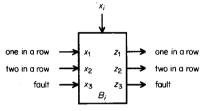

Solution The nature of the problem suggests an iterative approach. A typical block somewhere in the middle is considered first. This block  $B_i$  is shown in figure 2.33. The iterative inputs and outputs that come immediately to mind are 'no failures in a row', 'one failure in a row', 'two failures in a row' and 'three failures in a row' (or 'fault'). Now in passing from one block to the next, there is only one pattern of interest, which progressively goes from one to two to three failures. As far as the iterative outputs are concerned, the output 'no

Figure 2.33 Iterative block for example 2.11.

failures in a row' is of no interest, and so this variable is dropped from both input and output lines. The remaining iterative inputs and outputs are labelled, and  $x_i$  is applied at the top. The logic equations can be written directly from the desired pattern as

$$z_1 = x_i$$

$$z_2 = x_1 x_i$$

$$z_3 = x_3 + x_2 x_i$$

Note that  $z_2$  is not  $x_1x_i+x_2$ . The problem is not to detect that three bulbs have failed, but that three consecutive bulbs have failed. The above equations are readily realised in gate form.

# Example 2.12

Draw a four-variable Karnaugh map for the function  $z = x_2x_4 + x_1x_2\bar{x}_3\bar{x}_4 + \bar{x}_1\bar{x}_2\bar{x}_3x_4 + x_1\bar{x}_2x_3x_4 + \bar{x}_1x_2x_3\bar{x}_4$ . Find the essential prime implicants for this function.

#### Example 2.13

Design a logic circuit that goes to *one* whenever its three-variable input is palindromic  $(x_1 = x_3)$ . Realise this circuit with a minimum number of two-input NOR gates, assuming that the inverted inputs  $(\bar{x}_1, \bar{x}_2, \text{ and } \bar{x}_3)$  are not available externally. (Hint: see example 2.4.)

# Example 2.14

Design a combinational circuit that increments a three-bit input number  $x_1x_2x_3$  by one. For example,  $x_1x_2x_3 = 101$  would result in  $z_1z_2z_3 = 110$ . The number  $x_1x_2x_3 = 111$  should produce  $z_1z_2z_3 = 000$ . (Hint: make a chart showing all input and output combinations, and then construct a separate map for each z.)

#### Example 2.15

Tom dates girls who are over 21, have red hair, and are tall, or girls who are tall, not rich, have red hair, and are under 21, or girls who are over 21, rich and tall. Express Tom's preferences in the most economical manner.

#### Example 2.16

A four-bit binary number  $x_1x_2x_3x_4$  is used to represent a decimal digit between 0 and 9. Design a two-input NAND-gate circuit that will produce an output whenever the input is a prime number. Zero is not considered to be prime.

# Example 2.17

A logic circuit has an input consisting of a six-bit binary number  $x_1x_2 x_6$ . The circuit is to detect when any of the numbers 7, 9, 13, 23, 25, 27, 29, 34, 38, 39, 41, 45, 55, 57, 59 or 61 occur. The numbers 24 and 26 are don't cares. For example, the number 9 is  $x_1x_2x_3x_4x_5x_6 = 001001$ . Find the essential prime implicants for this circuit.

#### References

- Dietmeyer, D. L., *Logical Design of Digital Systems* (Allyn and Bacon, Boston, 1971) pp. 405–28.

- Hill, F. J., and Peterson, G. R., *Introduction to Switching Theory and Logical Design* (Wiley, New York, 1968) pp. 140–8.

- Lewin, D., Logical Design of Switching Systems (Nelson, London, 1968).

- Matheson, W. S., 'PCN Equivalence-class Invariants and Information Quantities', *I.E.E.E. Trans. Comput.*, C-20 (1971a) pp. 691–4.

- Matheson, W. S., 'Recognition of Monotonic and Unate Cascade Realizable Functions Using an Informational Model of Switching Circuits', *I.E.E.E. Trans. Comput.*, C-20 (1971b) p. 1214.

- Motorola, Analysis and Design of Integrated Circuits (McGraw-Hill, New York, 1968).

- Motorola, McMOS Handbook (Motorola Inc., Phoenix, Ariz., 1973).

- Petrick, S. R., On the Minimisation of Boolean Functions, Proc. Symp. Switching Theory, ICIP, Paris (1959).

- Potton, A., An Introduction to Digital Logic (Macmillan, London and Basingstoke, 1973).

# Introduction to Sequential Systems

# 3.1 Fundamental concepts

# 3.1.1 Defining features of sequential systems

The systems that have been discussed so far have been purely combinational. The fundamental property of such systems is that, at all times, all of the outputs are determined solely by the present instantaneous values of all the inputs. Of course, in a practical system, there will be some delay between an input change and the resulting changes in one or more of the outputs; but, when equilibrium is reached, a knowledge of all the inputs, together with the logical structure of the system itself, enables all of the outputs to be determined uniquely. In contrast, the outputs of sequential systems are determined not only by the present values of the inputs but also by their previous values.

Clearly, if the outputs are to depend on previous values of the inputs, the system must contain some elements that are capable of *storing* digital information. It is the presence of storage devices, of whatever kind, that distinguishes sequential systems from purely combinational ones.

# 3.1.2 Combinational and sequential interpretation of the problem specification

In some cases a system specification is inherently either combinational or sequential and can be realised only with a system of the appropriate type. Frequently, however, the specification can be interpreted by the designer either in terms of a combinational system or a sequential one. The former approach often has the advantage of speed whereas the latter can be more economical to realise.

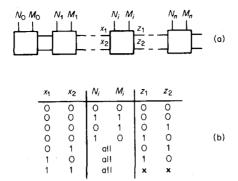

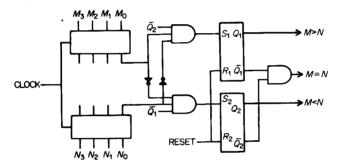

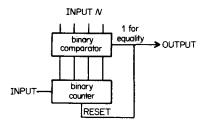

Consider, for example, the problem of comparing two binary numbers (N

and M). Three outputs are required; one  $(z_1)$  is to be logical *one* when N exceeds M, the second  $(z_2)$  is to be logical *one* when M exceeds N and the third  $(z_3)$  is to be logical *one* when N and M are equal. This problem is clearly amenable to a purely combinational solution. However, even if N and M are of only four bits each, listing all possible input combinations produces a truth table with  $2^4 \times 2^4 = 256$  rows and the minimisation problem is an eight-variable one.

Problems of this kind are often more amenable to an iterative approach, as discussed in chapter 2. It must be emphasised that this approach does not involve storage and, therefore, strictly falls into the category of combinational systems. But, since many of the concepts of iterative systems have their counterparts in truly sequential ones, a brief review of the iterative approach of section 2.5 would not be inappropriate here.

The direct combinational approach makes a simultaneous comparison of all the digits of both numbers. Using an iterative approach, the most significant digits of each number are compared first in a relatively simple circuit. There are four possible combinations of these two binary digits, of which three groups are relevant to the present problem

- (a) the most significant digit of N exceeds that of M;

- (b) the most significant digit of M exceeds that of N; and

- (c) the most significant digits are equal.

If either case (a) or case (b) applies, the relative magnitude of N and M is immediately determined and the remaining digits of the two numbers cannot influence this. If case (c) applies, the relative magnitude of N and M will be determined by the next (less significant) pair of digits unless they are also equal, in which case the third pair must be examined, and so on.

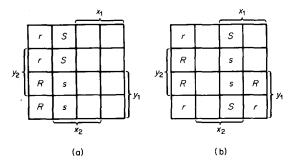

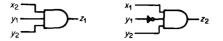

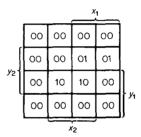

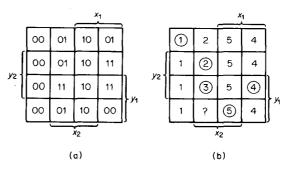

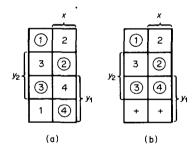

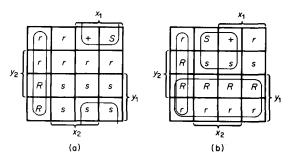

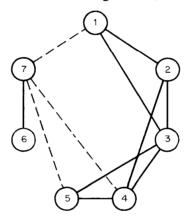

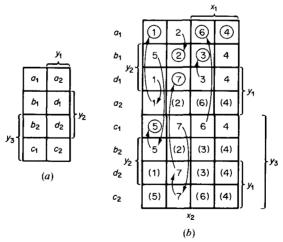

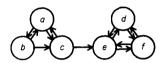

The advantage of this approach is that the relatively simple circuit that compares one pair of digits can be repeated for each subsequent pair and, if a design is to be modified to accept numbers containing more digits, it is merely necessary to add more 'cells' consisting of this basic circuit. As there are three distinct pieces of information to be handed on from one cell to the next, two connections will be required giving one redundant combination. One possible arrangement is given in figure 3.1a. The variables  $z_1$  and  $z_2$  that 'hand on' information concerning the relative magnitudes of previous digits are sometimes called the state variables. In this particular example,  $z_1z_2 = 00$  is chosen to indicate that all previous pairs of digits examined have been equal to each other,  $z_1 z_2 = 01$  indicates that M has already exceeded N and  $z_1 z_2 = 10$  indicates that N has exceeded M. Each cell produces a pair of updated state variables, in accordance with the truth table of figure 3.1b, which are handed on to the next cell. The required outputs, as defined previously, are obtained from the last cell and  $z_3 = \bar{z}_1 \bar{z}_2$ . The detailed design of one cell will be left as an exercise for the reader.

The iterative approach produces a system that is purely combinational since no storage elements have been introduced. In this sense, the use of the

Figure 3.1 Iterative approach to the comparison of two binary numbers. (a) Interconnection of cells. (b) Truth table for one cell.

term 'state variable' to describe the intermediate signals is misleading since this term is widely used in engineering and physics in relation to stored quantities, particularly energies (see, for example, Derusso *et al.*, 1967).

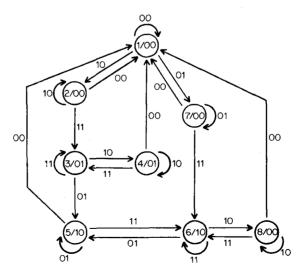

The final approach to the comparator problem is a truly sequential one. A single cell, having similar properties to the one discussed previously, is used to compare each pair of digits in turn, starting with the most significant. The results of each comparison must be stored in suitable devices and these stored values will in turn become inputs for subsequent comparisons. The process continues until all pairs of digits have been compared; details will be discussed later (example 3.5) when the required circuit elements have been considered.

The binary comparator can, therefore, be realised in any of the three forms discussed above. The direct combinational approach would be the fastest but would require the most hardware. The iterative system may or may not require less gates but the response time could be longer in view of the increased number of gate delays involved. The sequential system would be the slowest of all because each pair of bits is compared in turn but could well be the cheapest to implement—a good example of engineering compromise!

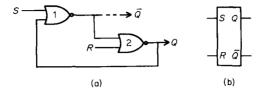

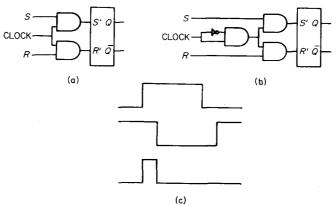

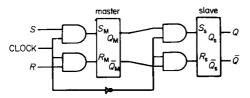

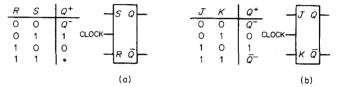

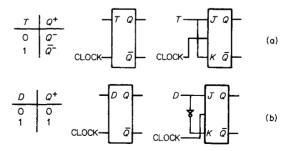

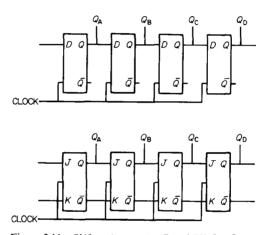

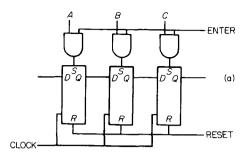

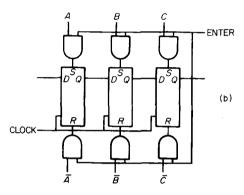

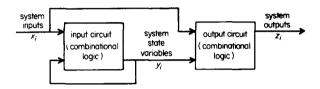

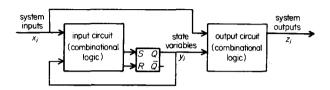

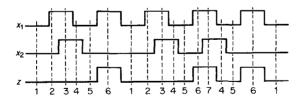

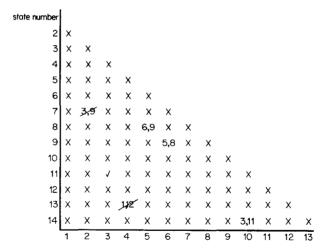

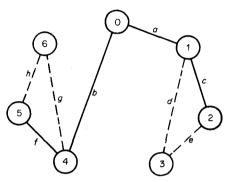

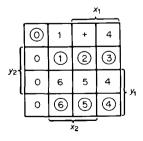

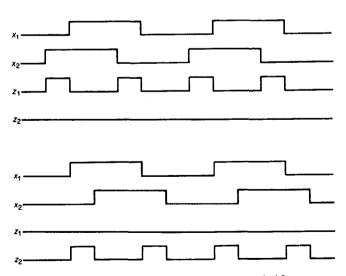

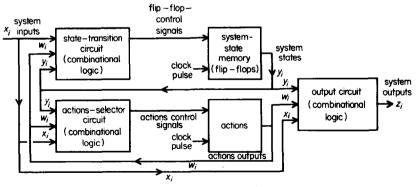

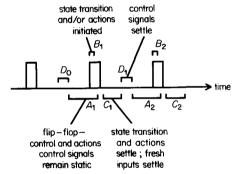

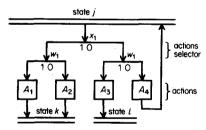

# 3.1.3 Synchronous and asychronous approaches to sequential-system design